## Fine Pitch Substrate for Cost Effective Flip Chip Package using Embedded Trace Substrate Technology

Dr. Kay Essig

ASE Europe May 21, 2014

## **EPP Substrates**

- ASE Substrate Manufacturing

- Substrate manufacturing

- Subtractive

- MSAP/ SAP

- EPP

- Cu pillar FlipChip fine pitch

- Peripheral, Array, Pitches on Substrate

- Reliability Results

- Wire Bond Finger Pitch (Hybrids)

- Conclusion

## **Substrate Manufacturing Sites**

THNOLOGY

## **Substrate Manufacturing Sites**

ECHNOLOGY

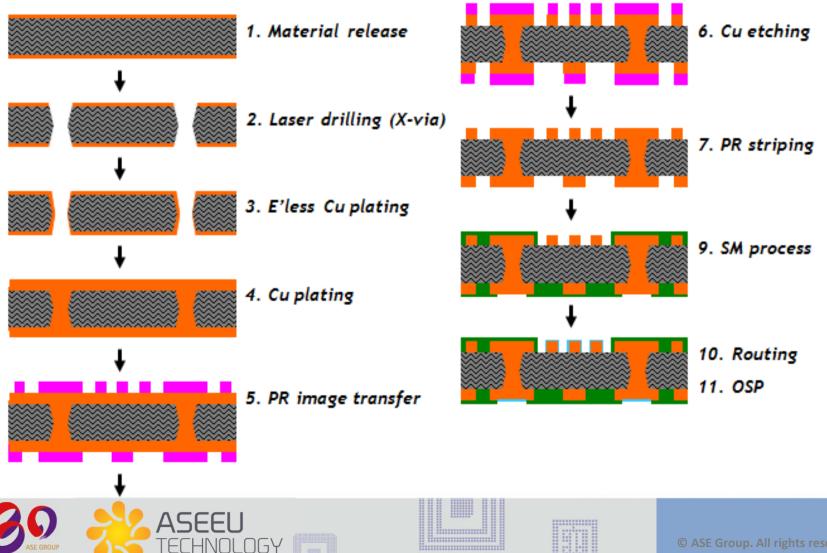

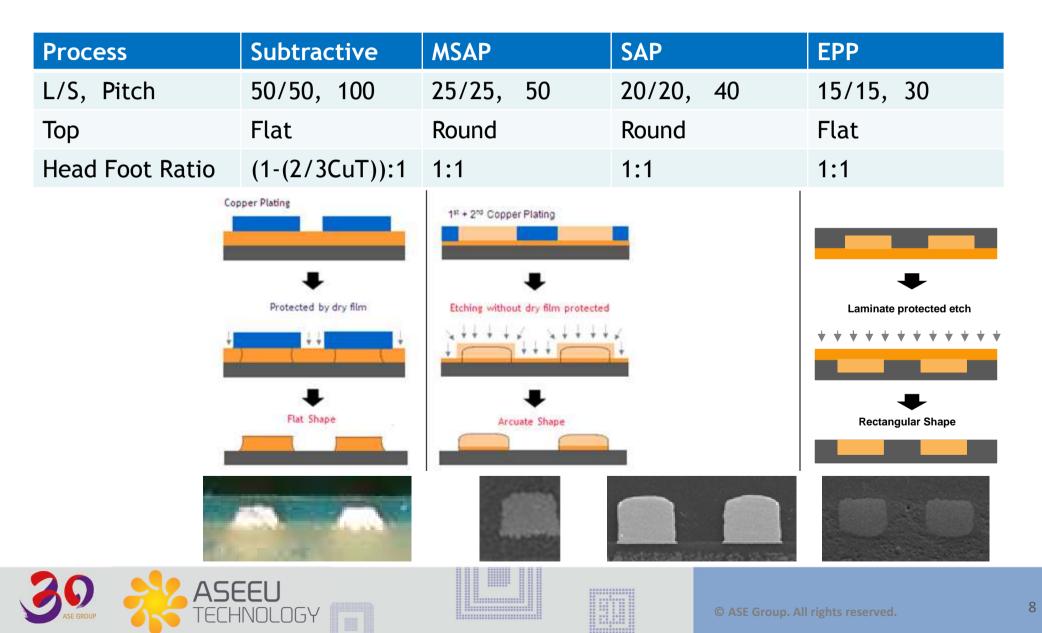

#### Subtractive

- Via drill, E'less Cu, Panel Plating, Tent'n'Etch

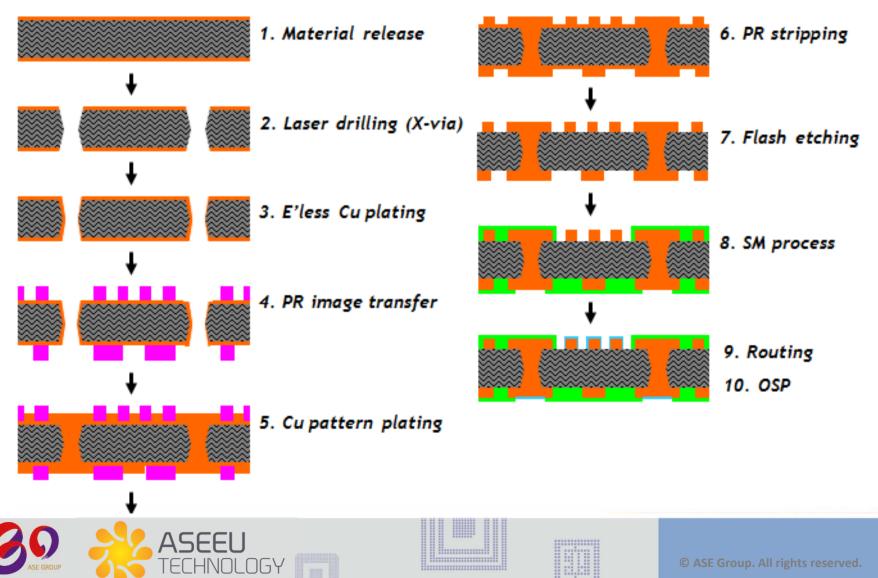

### • MSAP (Modified Semi Additive Process), SAP

#### - Via drill, E'less Cu, Pattern Plating, Flash Etch

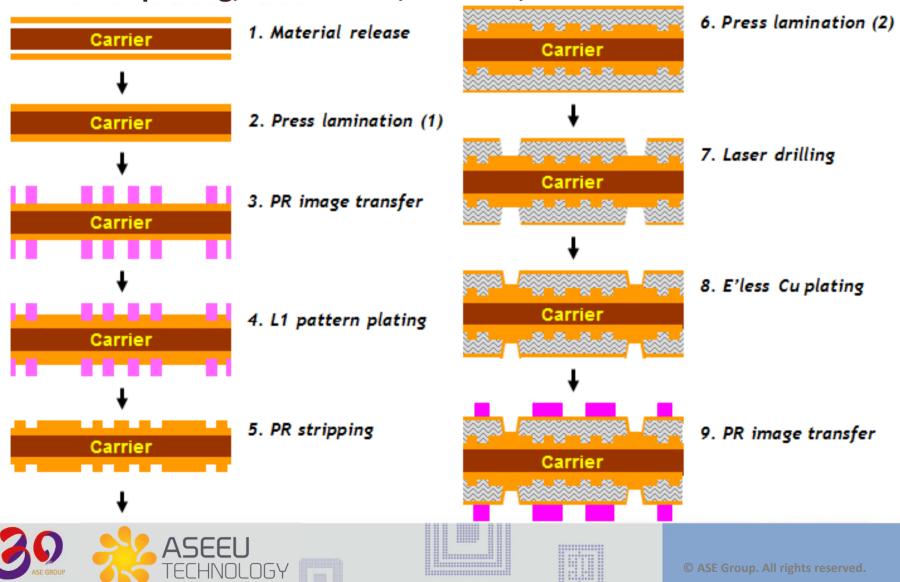

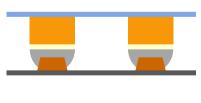

### • EPP (Embedded Pattern Process) I

- Pattern plating, Lamination, Via Drill, E'less Cu

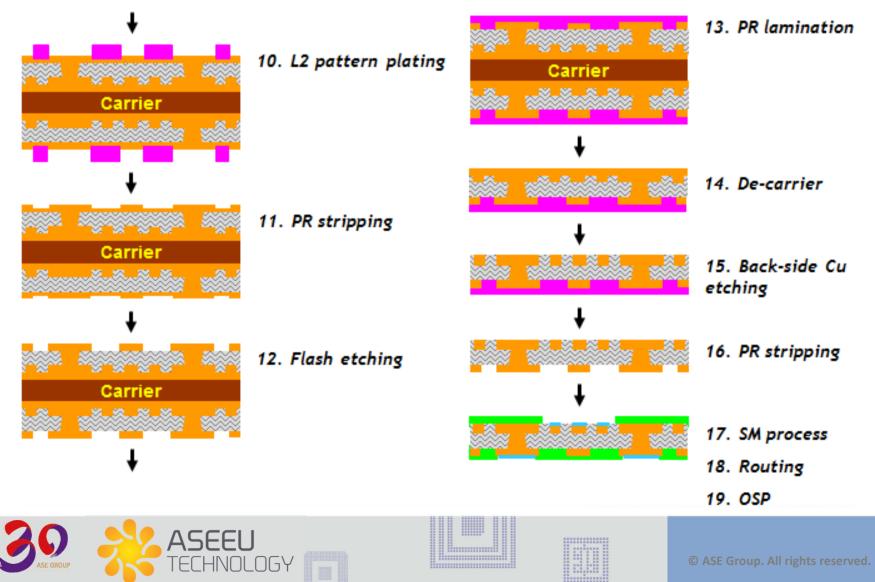

### • EPP (Embedded Pattern Process) II

- Pattern plating, Flash Etch, De-carrier, Backside Etch

7

#### • Subtractive vs. MSAP vs. SAP vs. EPP

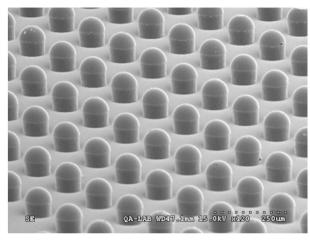

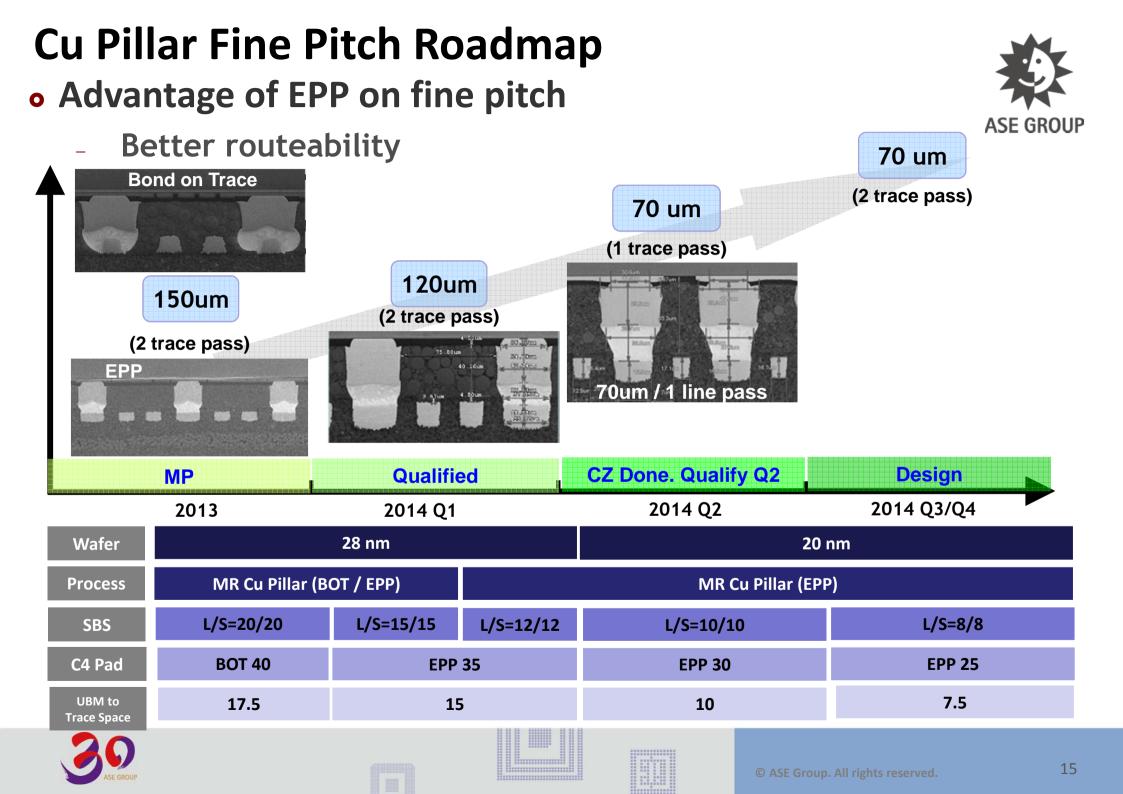

# **Fine Pitch Bumping**

- N40nm / N28nm / N20nm wafer node and beyond

- Small Die Size

- High I/O Count

- Small Pitches

- FC Bumping Pads

- Wire Bond Pads

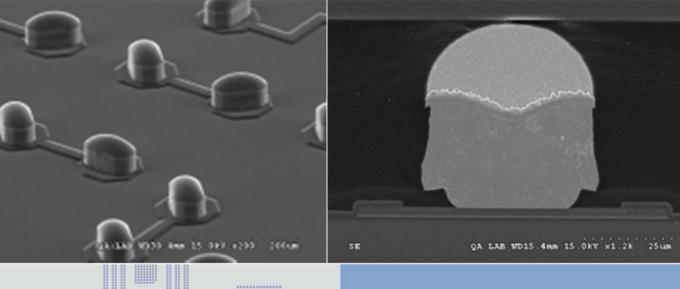

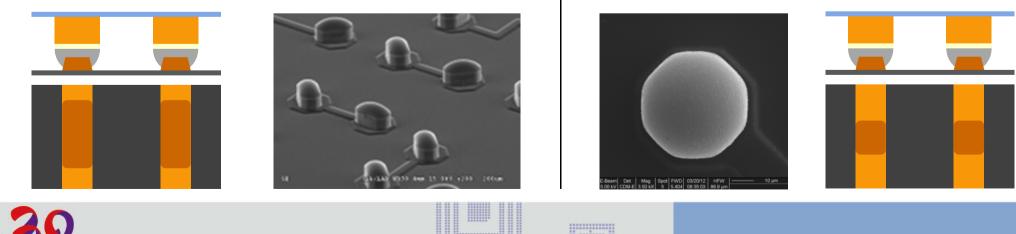

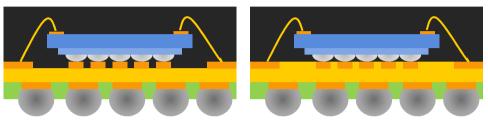

## • CuBOL (Cu Pillar Bond On Line)

- Solder Cap of Cu Pillar encroaches the Cu Trace on Substrate

- Trace Volume adds to the Solder Cap Volume

- Solder Cap Volume expands

- Along the Trace

- Perpendicular to the Trace

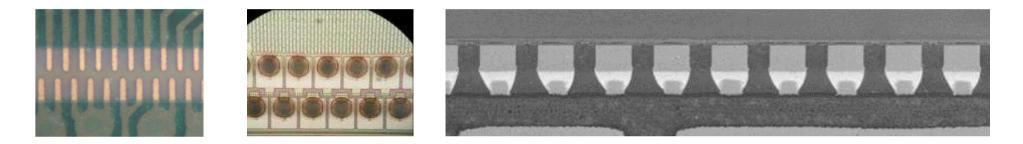

## • FC MR MUF (FlipChip, Mass Reflow, Mold Under Fill)

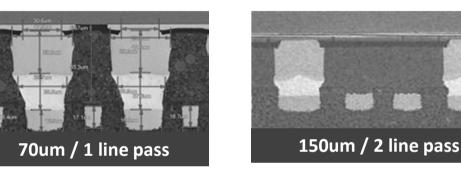

- 2 Rows Peripheral Cu Pillar Bumps 60um Pitch each row

3 and more Rows Cu Pillar Bumps have the need of traces routing between bond pads. These traces can not be covered by Solder Mask

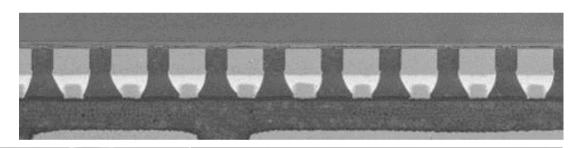

### CuBOL on EPP Substrate

- Solder Cap of Cu Pillar wets the Cu Trace Top on EPP Substrate

- Trace Volume does not add to the Solder Cap Volume

#### • Oval or Bar shape Cu Pillar enlarges the Solder Bond Area

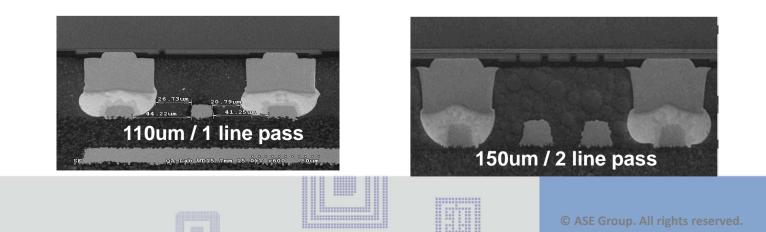

- Reliability comparison CuBOL vs. CuBOL EPP Substrate

- Device 11.8x11.8 mm<sup>2</sup>, 515 Balls, Die 6.6x5 mm<sup>2</sup>,

899 oval Cu pillar 45x95, pitch 150 um with 2 lines pass

| Device<br>Version | MSL3/2aa | ТСВ 1000<br>сус | HAST 96<br>hrs | ТСТ 3500<br>сус | HTST 3000<br>hrs |

|-------------------|----------|-----------------|----------------|-----------------|------------------|

| CuBOL             | Pass     | Pass            | Pass           | Pass            | Pass             |

| CuBOL EPP         | Pass     | Pass            | Pass           | Pass            | Pass             |

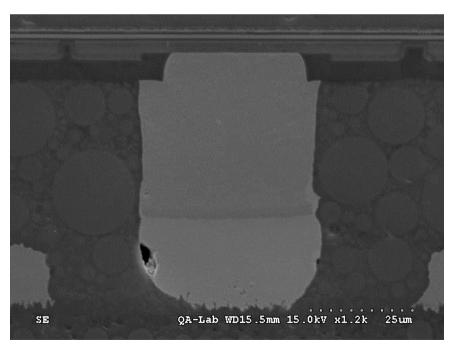

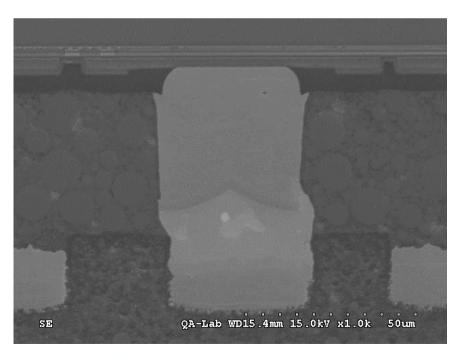

### • Reliability comparison CuBOL vs. CuBOL EPP

- Comparison after TCT 3500 Cycles

#### CuBOL – Cu Trace no longer oberservable

CuBOL EPP – Half of the Cu Trace diluted

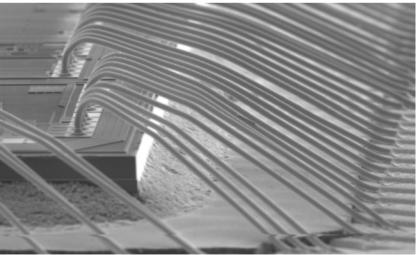

# **Bond Finger Pitch**

- Hybrid Packages with Wire Bond Die on Top

- Bond Finger Pitch

- Bond Finger Top Width

|               | Process | Head | Foot | Pitch |

|---------------|---------|------|------|-------|

|               | Sub     | 40   | 55   | 85    |

| 0un - 51.48un | MSAP    | 40   | 50   | 80    |

|               | EPP     | 40   | 40   | 60    |

| 20            |         |      |      |       |

# Conclusion

• EPP Substrates as a result of coreless substrates can be manufactured in any layer count with flexible via connections from layer to layer – high routability

• Embedded Traces result in finer pitches for Cu pillar FC assembly as well as for wire bond and hybrid assembly

• Slower IMC formation due to only one contact surface to the Copper Pillar solder cap; expect similar reliability test results

• EPP Substrates can be a good solution when ultra fine pitch Cu Pillar Flip Chip is requested.

# **Thank You**

www.aseglobal.com